Представлена технология для энергоэффективных 2-нм чипов за авторством IBM и Rapidus

Arkadiy Andrienko

Arkadiy Andrienko

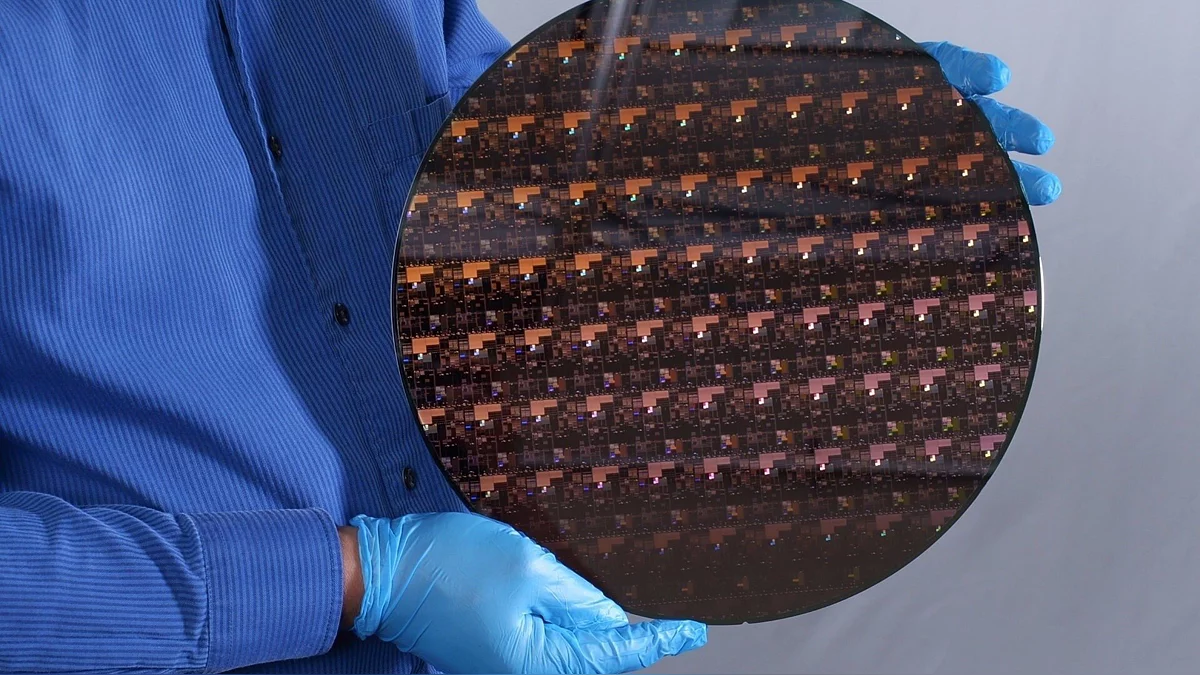

На конференции IEDM 2024 компании IBM и Rapidus представили важное достижение в области полупроводников. Партнёры анонсировали успешное продвижение к массовому производству 2-нм чипов, разработав методы для выпуска как высокопроизводительных, так и энергоэффективных модификаций этих чипов. Ожидается, что до конца десятилетия эти технологии будут реализованы на заводе компании Rapidus в Японии.

В ходе конференции были представлены инновационные методы производства, включая использование GAA-транзисторов с несколькими пороговыми напряжениями для различных типов устройств. Это позволяет создавать чипы с высокой производительностью для мощных систем и с низким энергопотреблением для мобильных или энергоэффективных решений. Особое внимание было уделено технологии выборочного уменьшения слоя (Selective layer reductions, SLR), которая позволяет точно контролировать пороговое напряжение в зависимости от толщины промежутка между полупроводниковыми каналами.

Важным достижением стало также снижение загрязнения подложки чипов ионов в процессе травления, что повысило чистоту производства и позволило уменьшить дефекты в конечных продуктах. Генеральный менеджер Rapidus US, отметил, что внедрение мультипороговых напряжений (Multi-Vt) в архитектуру чипов стало ключевым этапом развития компании и уверенно продвигает её к реализации амбициозных целей по созданию передового полупроводникового завода на Хоккайдо.

С развитием технологий производства 2-нм чипов, будущие процессоры смогут предложить как рекордную производительность, так и энергоэффективность, что откроет новые горизонты для мобильных устройств, компьютеров и других технологий.

-

![]() Лиза Су предсказывает смену GPU на ИИ-чипы в течение пяти лет

Лиза Су предсказывает смену GPU на ИИ-чипы в течение пяти лет -

![]() Intel и AMD объединяются для совместной работы над x86-чипами

Intel и AMD объединяются для совместной работы над x86-чипами -

![]() Maxwell Labs обещает революцию в охлаждении чипов

Maxwell Labs обещает революцию в охлаждении чипов -

![]() AMD запатентовала новый метод укладки чиплетов для увеличения производительности

AMD запатентовала новый метод укладки чиплетов для увеличения производительности -

![]() Neuralink тестирует управление роборукой через мозговой чип

Neuralink тестирует управление роборукой через мозговой чип